Peaki duty cycle az olduğunda ve çıkışta aynı yük varken peakler de sıçrama oluyor mu ? Yoksa sadece duty cycle yükseldiğinde mi yapıyor. Koyduğun resimde cross conduction var. Yani daha önce dediğim gibi sarı ve mavi voltajların biri tam 0 olmadan diğeri yükseliyor. Bridge topolojilerinde kesinlikle cross conduction olmaması lazım fakat push pullda da yine max olarak %40 olarak açılması lazım duty cycle ın. Yani bu iki transistör için toplamda %80 eder. Kitaplara tekrar baktım. Senin peaklerin nedeni leakage inductance da olabilir. Primerde iki tane birbirine seri sarım ve bunların herbirine de seri leakage inductance olduğu için bu yüzden push pull da peak voltajları fazla oluyor. Hatta transistörlerin bile 1.3 x 2Vdc ye göre seçilmeleri gerekiyor. Vdc = DC giriş voltajı. Yani hem devredeki fazla endüktanstan kaynaklanıyor hatta daha önemlisi trafoyu nasıl sardığında önemli. Bunlar hep kritik rol oynuyor smpslerde.

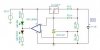

Şimdi senin soruna tekrar gelirsek, transistörleri nasıl sürdüğünü araya ne kadarlık direnç koyduğunu bilmiyorum. Transistörleri daha hızlı off yapabilmek için dirençlere paralel hızlı diyot koy, cathode kısmı entegre çıkışlarına bakıcak şekilde. O dirençler 4R ile 27R arasında olabilir, çok yüksek değer koyma. Dediğim kapasitör voltaj kontrollü smps lerde nüvenin saturasyonunu engellemek için. Bu push pull da dc kaynak ile trafonun orta ucu arasına koyulur diye hatırlıyorum. Kitaplara baktığımda kapasitörün push pull da nereye konması gerektiğini söylememiş sadece seri olacak demiş primere. Bu eski bir teknik olduğu için yeni kitaplarda bu kapasitöre bile değinmiyor direk akım kontrollü kullanın diye yazıyor. Fakat bu kapasitör kutupsuz olmalı ve hesabı var, hesabını bulursam koyarım. Yalnız saturasyonunu yüzde yüz engelleyemediği durumlarda oluyor.

Son olarak bu doğrusal olarak gecikmelerin sebebi, mosfetin gate ucunun kapasitansının olması ve bunu normal kapasitör gibi düşünürsen, bunları ne kadar hızlı şarj edip, deşarj edersen o kadar hızlı anahtarlama yaparsın. Bağladığın dirençler yüksek gibi sanki, onun için onları 4R ile 27R arasına çekersen sorunun düzeleceğini düşünüyorum. Eğer hiç düzelmiyorsa, entegre uçlarına totem pole yada hızı artırmak için bazı düzenlemeler yapabilirsin. Hatta buralara yüksek değerde direnç bağlaman voltajda osilasyona bile sebebiyet verebilir. Bunu şimdi hatırladım